| <b>FF000</b>                            |

|-----------------------------------------|

| EE282                                   |

| Computer Architecture                   |

| ·                                       |

| Lecture 3:                              |

|                                         |

| Instruction-Set Architecture (Part 2)   |

| October 4th, 2001                       |

|                                         |

| Marc Tremblay                           |

| Stanford University                     |

| marctrem@csl.stanford.edu               |

|                                         |

| WJD/AW/MT<br>EE282 - Class 3 – 10/04/01 |

| Orientian                                                                                                                                                                                                 |                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Operations <ul> <li>arithmetic</li> <li>logical</li> <li>data type conversions</li> </ul> </li> <li>Data Movement <ul> <li>memory reference</li> <li>register to register</li> </ul> </li> </ul> | <ul> <li>Control <ul> <li>what instruction to do next</li> <li>tests (compare)</li> <li>branches and jumps</li> <li>support for procedure call</li> <li>operating system entry</li> </ul> </li> <li>Misc. Junk</li> </ul> |

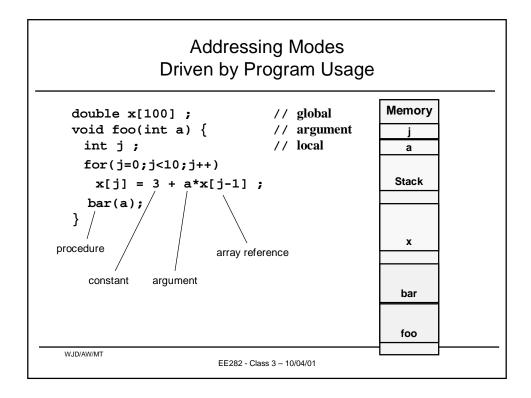

| Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <ul> <li>Stack relative for locals and arguments         <ul> <li>*(R30+x)</li> <li>a, j</li> </ul> </li> <li>Short immediates (small constants)         <ul> <li>3</li> </ul> </li> <li>Long immediates (global addressing)             <ul> <li>&amp;x[0], &amp;bar</li> <li>&amp;x3ac1e400</li> </ul> </li> <li>Indexed for array references         <ul> <li>*(R4+R3)</li> <li>*(R4+R3*S)</li> </ul> </li> </ul> | Memory<br>j<br>a<br>Stack<br>x<br>bar<br>foo |

| WJD/AW/MT EE282 - Class 3 – 10/04/01                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

|           |                        | essing Moo |           |

|-----------|------------------------|------------|-----------|

| #n        | immediate              | @d(Rn)[Rx] |           |

| Rn        | Register               | @#addr[Rx] |           |

| (Rn)      | Direct                 | (PC)+      | immediate |

| -(Rn)     | predecrement           | @(PC)+     | absolute  |

| (Rn)+     | postincrement          | @d(PC)+    | immediate |

| @(Rn)+    | Indirect postincrement |            |           |

| d(Rn)     | Displacement (b,w,l)   |            |           |

| @d(Rn)    |                        |            |           |

| (Rn)[Rx]  | Indexed                |            |           |

| (Rn)+[Rx] |                        |            |           |

| -(Rn)[Rx] |                        |            |           |

| @(Rn)+[Rx | :]                     |            |           |

| d(Rn)[Rx] |                        |            |           |

|           |                        |            |           |

| Control III                                                                                                                                                                                                                                                       | structio | 115  |                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------------------------------------------|

| Implicit control on each     instruction                                                                                                                                                                                                                          | LOOP:    | LOAD | R1 <- *(R5+R2)                            |

| $IP \leftarrow IP + 4$                                                                                                                                                                                                                                            | 2001.    | ADD  | R3 <- R3 + R1                             |

| • Unconditional jumps<br>$IP \leftarrow X$<br>$IP \leftarrow IP + X$<br>X can be constant or register<br>• Conditional jumps (branches)<br>$IP \leftarrow IP + ((\text{cond})? X : 4)$<br>• Predicated instructions<br>• Conditions<br>- flags<br>- in a register |          | ADD  | R2 <- R2 + 4<br>R4 <- R2 == 8<br>R4, LOOP |

|                                                                                                                                                                                                                                                                   |          | CMP  |                                           |

|                                                                                                                                                                                                                                                                   |          | JNE  |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

|                                                                                                                                                                                                                                                                   |          |      |                                           |

| <ul> <li>fused compare and branch</li> </ul>                                                                                                                                                                                                                      |          |      |                                           |

| Next Time                                                                                             |  |  |

|-------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Implementation</li> <li>building blocks</li> <li>simple implementation of the DLX</li> </ul> |  |  |

| WJD/AW/MT EE282 - Class 3 – 10/04/01                                                                  |  |  |