- Key idea: add instruction support to speed up media tasks

First used in Intel i860 ('89) -- 6 instructions for 3D triangle rendering and the HP

PA7100LC (circa 90) -- 5 instructions using implementation-specific features

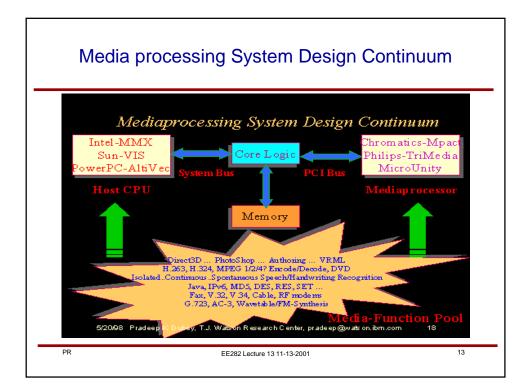

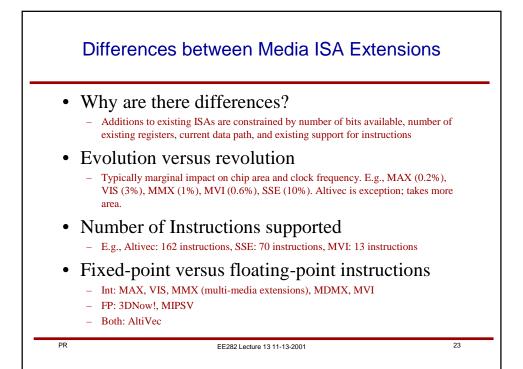

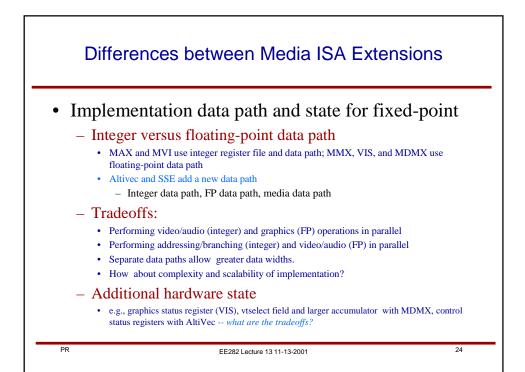

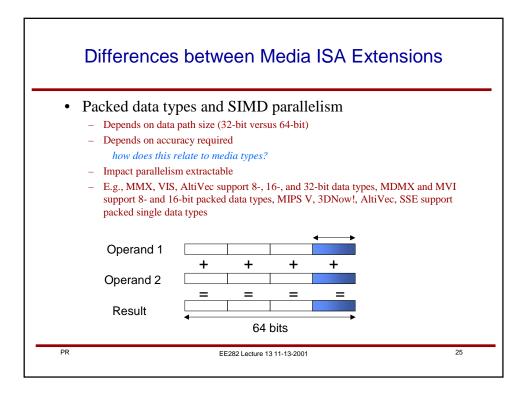

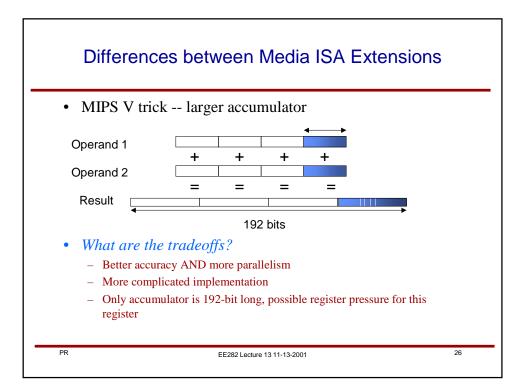

Integer/Fixed-point extensions

HP MAX (Media Acceleration extensions), Sun VIS (Visual Instruction Set), Intel/Cyrix/AMD MMX

(multi-media extensions), MIPS Digital Media Extensions), Digital MVI (Motion Video

Extensions), (IBM/Motorola) PowerPC AltiVec technology

Floating-point extensions

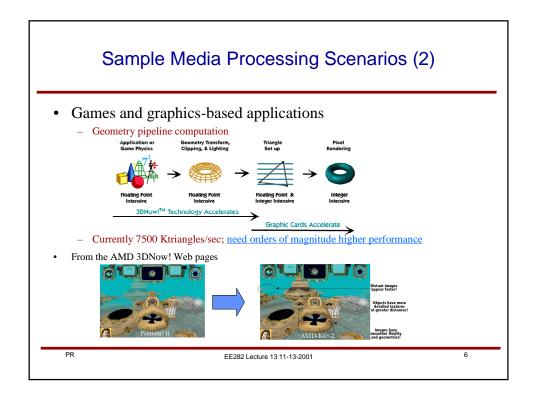

AMD 3DNow!, Intel SSE (internet and streaming extensions), MIPS V extensions, PowerPC AltiVec

Constraints: ISA changes affect all levels of architecture

Need to have significant performance benefits for target applications

No adverse performance impact on other applications

- Scaleable benefits and implementation complexity in future

PR

EE282 Lecture 13 11-13-2001

15

| Arithmetic                                                                       | PADD[B,W,D],PADDS[B,W],PADDUS[B,W],                                                                                                                                                                    |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  | PSUB[B,W,D],PSUBS[B,W,D], PSUBUS[B,W],<br>PMULHW, PMULLW, PMADDWD                                                                                                                                      |

| Comparison                                                                       | PCMPEQ[B,W,D],PCMPGT[B,W,D]                                                                                                                                                                            |

| Conversion                                                                       | PACKUSWB,PACKSS[WB,DW],PUNPCKH[BW,WD<br>,DQ], PUNPCKL[BW,WD,DQ]                                                                                                                                        |

| Logical                                                                          | PAND, PANDN, POR, PXOR                                                                                                                                                                                 |

| Shift                                                                            | PSLL[W,D,Q], PSRL[W,D,Q], PSRA[W,D]                                                                                                                                                                    |

| FP and MMX state mgt                                                             | EMMS                                                                                                                                                                                                   |

| Data Transfer                                                                    | MOV[D,Q]                                                                                                                                                                                               |

| Use FP registers, 32-bit<br>re information availab<br>" <u>MMX Technology Ov</u> | lows the classification discussed in previous slides<br>data path, SIMD, saturation, conditional moves<br>ole from<br><u>erview</u> ", Intel web site.<br><u>c.intel.com/drg/mmx/manuals/overview/</u> |