### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2002/0049901 A1

Apr. 25, 2002 (43) Pub. Date:

#### (54) SYSTEM AND METHOD FOR IMPLEMENTING SOURCE BASED AND EGRESS BASED VIRTUAL NETWORKS IN AN INTERCONNECTION NETWORK

(75) Inventor: Philip P. Carvey, Bedford, MA (US)

Correspondence Address: James M. Smith, Esq. HAMILTON, BROOK, SMITH & REYNOLDS, P.C. Two Militia Drive Lexington, MA 02421-4799 (US)

Assignee: Avici Systems, Inc., North Billerica, MA

(21) Appl. No.: 09/866,335

May 25, 2001 (22) Filed:

#### Related U.S. Application Data

Non-provisional of provisional application No. 60/234,399, filed on Sep. 21, 2000.

#### **Publication Classification**

Int. Cl.<sup>7</sup> ...... H04L 9/00 (52)

#### **ABSTRACT**

An interconnection network, particularly a Gamma graph network, comprising a number of interconnected routers implementing source based and egress based virtual networks in order to prevent tree saturation and deadlock while routing packets. The interconnection network can be used as a fabric within a multi-application switch router, for example. Packets traverse the fabric from any packet source to any packet destination by traversing a source based virtual network associated with a packet source and then by traversing an egress based virtual network associated with a packet destination. By partitioning the fabric into source based virtual networks and egress based virtual networks, the number of control structures required to manage them are reduced as compared with destination based virtual network architectures. Furthermore, by dynamically assigning buffer resources to a virtual network when needed provides more efficient utilization of buffer resources as opposed to dedicated assignment of buffer resources to each virtual network.

F19. 1

F19.2

F19.4

F19.6A

F14. 7A

### ADJACENCY TABLES FOR NODES IN FIG. 7A

| AB                                                                                   | AC                                                                                   | AD                                                                                   |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| $AB \rightarrow BC$                                                                  | $AC \rightarrow CB$                                                                  | $AD \rightarrow DB$                                                                  |

| $AB \rightarrow BD$                                                                  | $AC \rightarrow CD$                                                                  | $AD \rightarrow DC$                                                                  |

| $AB \rightarrow BA$                                                                  | $AC \rightarrow CA$                                                                  | $AD \rightarrow DA$                                                                  |

| BA                                                                                   | ВС                                                                                   | BD                                                                                   |

| $BA \rightarrow AC$                                                                  | $BC \rightarrow CD$                                                                  | $BD \rightarrow DA$                                                                  |

| $BA \rightarrow AD$                                                                  | $BC \rightarrow CA$                                                                  | $BD \rightarrow DC$                                                                  |

| $BA \rightarrow AB$                                                                  | $BC \rightarrow CB$                                                                  | $BD \rightarrow DB$                                                                  |

| CA                                                                                   | СВ                                                                                   | CD                                                                                   |

| CA                                                                                   | Ų LJ                                                                                 |                                                                                      |

| CA → AB                                                                              | $CB \rightarrow BD$                                                                  | $CD \rightarrow DA$                                                                  |

|                                                                                      | •                                                                                    |                                                                                      |

| $CA \rightarrow AB$                                                                  | $CB \rightarrow BD$                                                                  | $CD \rightarrow DA$                                                                  |

| $CA \rightarrow AB$<br>$CA \rightarrow AD$                                           | $CB \rightarrow BD$ $CB \rightarrow BA$                                              | $CD \rightarrow DA$<br>$CD \rightarrow DB$                                           |

| $CA \rightarrow AB$ $CA \rightarrow AD$ $CA \rightarrow AC$                          | $CB \rightarrow BD$ $CB \rightarrow BA$ $CB \rightarrow BC$                          | $CD \rightarrow DA$ $CD \rightarrow DB$ $CD \rightarrow DC$                          |

| $CA \rightarrow AB$ $CA \rightarrow AD$ $CA \rightarrow AC$ $DA$                     | $CB \rightarrow BD$ $CB \rightarrow BA$ $CB \rightarrow BC$ $DB$                     | $CD \rightarrow DA$ $CD \rightarrow DB$ $CD \rightarrow DC$ $DC$                     |

| $CA \rightarrow AB$ $CA \rightarrow AD$ $CA \rightarrow AC$ $DA$ $DA \rightarrow AB$ | $CB \rightarrow BD$ $CB \rightarrow BA$ $CB \rightarrow BC$ $DB$ $DB \rightarrow BA$ | $CD \rightarrow DA$ $CD \rightarrow DB$ $CD \rightarrow DC$ $DC$ $DC \rightarrow CA$ |

FIG. 7B

F14.8A

F19. 88

F19,9

F19, 12

| CONTROL STRUCTURE    | SIZE (IN BITS)   | DESCRIPTION                                                                                                                                                                                                                   |

|----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ingress Packet State | 1280x35=44,800   | Each IngressPacketState structure manages the storage of a partially received packet on one of the ingress ports.                                                                                                             |

| EgressLaneState      | (128x30=3,480)   | Each EgresslaneState structure supplies information used to process received Credits.                                                                                                                                         |

| AvailableEgressLane  | (128x!)          | Each flag indicates that a particular lane is available or in use.                                                                                                                                                            |

| FanState             | (512x44=22,528)  | Each FanState structure holds one FAN waiting to be converted into a FIR and pointers which allow creating a linked list of packets waiting on a particular channel and a linked list of FANs comprising a particular packet. |

| AvailableFanState    | (512x1)          | Each flag indicates that a particular local FanState structure is availably or in use.                                                                                                                                        |

| WaitingForlanes      | (2928×1)         | Each flag indicates that a particular tunnel segment has a packet ready to be assigned to a lane as soon as one becomes available.                                                                                            |

| WaitingForFSM        | (2928x1)         | Each flag indicates that a particular channel has a FAN ready to be converted into a FIR as soon as the EgressController has bandwidth available to perform the conversion.                                                   |

| WaitingForFuFtfo     | (2304x1)         | Each flag indicates that a particular lane has a FAN ready to convert into a FIR as soon as room in the FIR FIFO becomes non-full.                                                                                            |

| SegmentPointer       | (2938x13=38,194) | Each SegmentPointer points to a a queue of packets waiting on a runnel segment.                                                                                                                                               |

FIG. 13

#### SYSTEM AND METHOD FOR IMPLEMENTING SOURCE BASED AND EGRESS BASED VIRTUAL NETWORKS IN AN INTERCONNECTION NETWORK

#### RELATED APPLICATION

[0001] This application claims the benefit of U.S. Provisional Application No. 60/234,399, filed on Sep. 21, 2000. The entire teachings of the above application are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] Interconnection networks are employed to forward messages between system elements in large computer and communication systems. The Internet is an interconnection network in which long messages are segmented into shorter units of information called packets which are then forwarded across the network independently through Internet routers. PCT Patent Application Ser. No. PCT/US98/16762, entitled "Router with Virtual Channel Allocation," filed Aug. 20, 1998, and published as WO99/11033, teaches an Internet router that includes an internal interconnection network referred to as a fabric. Fabrics overcome the port and bandwidth limitations commonly associated with routers that are based on common bus or crossbar switch topologies.

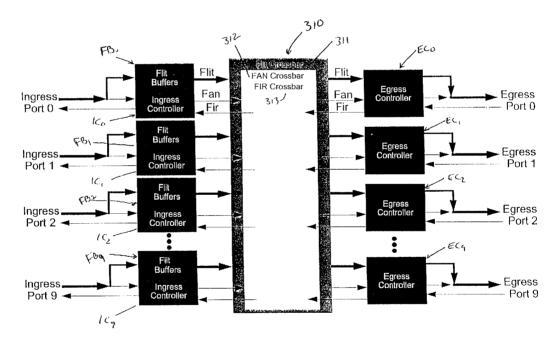

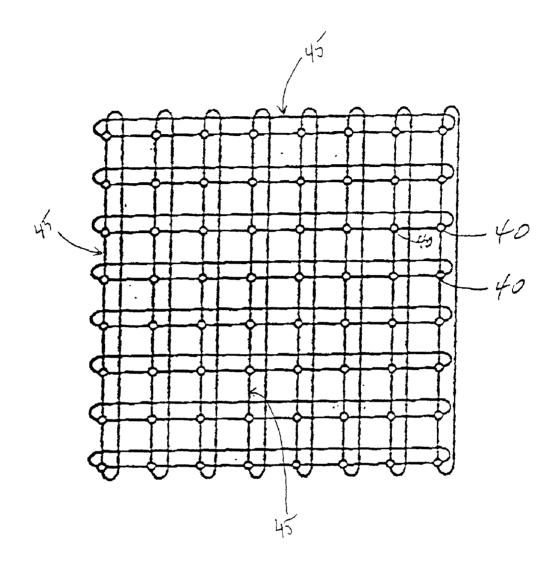

[0003] FIG. 1 illustrates a two dimensional torus array network which may serve as a fabric. The fabric is composed of a number of nodes 40, referred to as fabric routers, which are interconnected by fabric links 45. A fabric connects a group of external links, each coupled to a fabric router, and performs message routing and forwarding among the links. Data packets may be segmented into fixed length blocks called flow control units or flits. Flits are forwarded across the fabric using a technique called wormhole routing such that the head flit of the packet establishes a path through the fabric that is followed by the remaining flits of the packet.

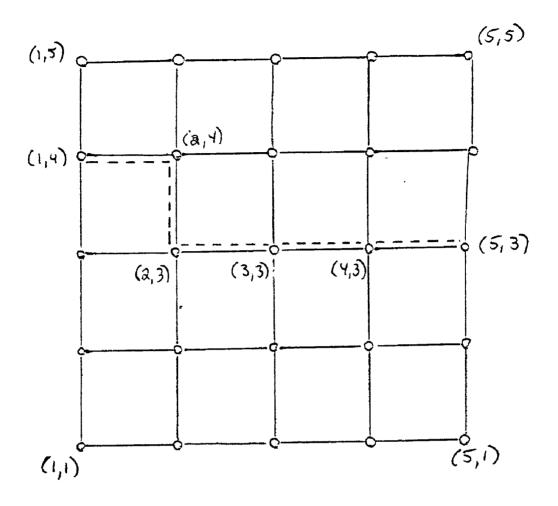

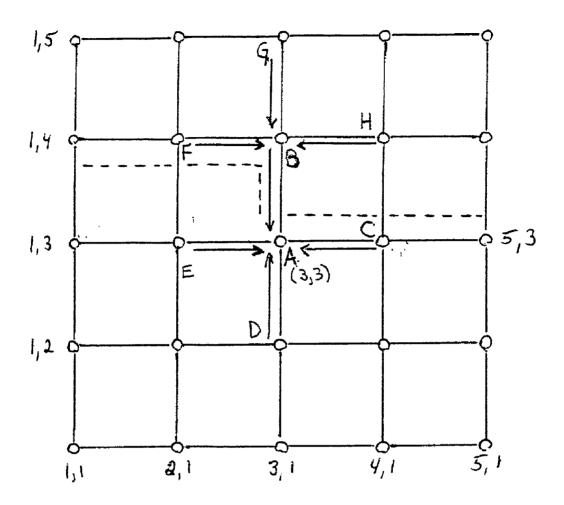

[0004] FIG. 2 illustrates packet traversal over a path through a fabric. A data packet arriving on an external link is forwarded through the fabric to an external destination link by transmitting the packet over a path comprising a series of interconnected fabric routers. For example, the data packet received on node (1,4) and destined for node (5,3) may traverse a path including nodes (1,4), (2,4), (2,3), (3,3), (4,3), and (5,3). The entire path can be computed by a fabric management microprocessor at the source node, which determines the most efficient path through the fabric. The calculated path is then specified within a fabric header appended to the packet. Alternatively, a path can be computed incrementally such that each path segment is determined by a fabric management processor at each fabric hop along the path to a destination link.

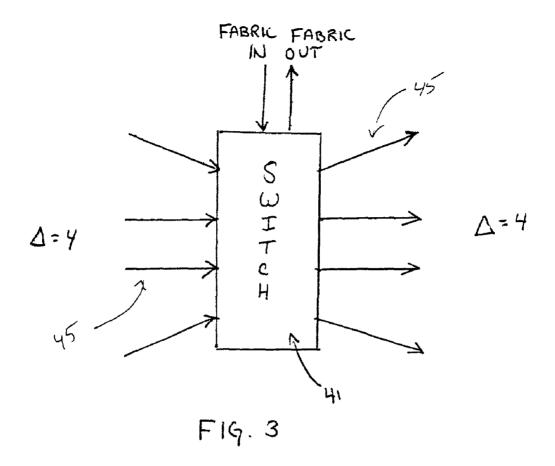

[0005] FIG. 3 illustrates a typical switch element of a fabric router for forwarding data packets. A fabric router typically includes one or more switch elements 41 for forwarding data packets. The switch forwards packets received on a switch ingress port to a switch egress port. The switch radix ( $\Delta$ ) of a fabric corresponds to the number of fabric links 45 fanning into a switch as well as the number of fabric links 45 fanning out of the switch. For example, the switch radix is equal to 4 in FIG. 3. Fabric links fanning into a switch are connected via switch ingress ports, while fabric links fanning out of a switch are connected via switch egress

ports. The remaining switch ingress ports and switch egress ports typically connect to external links (i.e., FABRIC IN and FABRIC OUT) coupled to the fabric via a line interface.

[0006] The total number of nodes in a fabric is called its size. Since the radix A of a switch is typically much smaller than the desired size in large fabrics, a packet will typically hop across multiple switch elements in order to traverse a fabric. The maximum number of links (i.e., hops) traversed by a packet from any source node to any destination node is called the diameter (D) of the fabric. Referring back to FIG. 2, the fabric size is 25 nodes and the diameter of the fabric is 8 hops. If the 25 nodes of

[0007] FIG. 2 were connected in a torus as illustrated in FIG. 1, the diameter would be reduced to 4 hops.

[0008] When packets have random destinations, the aggregate fabric bandwidth must be greater than the product of average diameter  $(D_{avg})$  multiplied by the aggregate ingress access bandwidth. Since the cost of a fabric is almost directly proportional to the aggregate fabric bandwidth required, fabric topologies which reduce the average diameter for a given size result in lower fabric costs.

#### SUMMARY OF THE INVENTION

[0009] Multicomputers and multiprocessors have for many years employed interconnection networks to send addresses and data for memory accesses between processors and memory banks or to send messages between processors (e.g., Inter-Processor Communication (IPC) messages). Early systems were constructed using bus and crossbar interconnects. However, to permit these machines to scale to larger numbers of processors, bus and crossbar interconnects were replaced with multi-hop direct and indirect interconnection networks. Recently, interconnection networks similar to those employed in multicomputer systems have been employed as switches and routers in the communication application space. For example, an Internet router, described in PCT Patent Application Serial No. PCT/US98/16762, entitled "Router with Virtual Channel Allocation," filed Aug. 20, 1998, and published as WO99/11033, is implemented by a three-dimensional torus array fabric.

[0010] While multi-hop interconnection networks are scalable, they lack two desirable features of crossbar-based routers: tree saturation free operation and stiff backpressure. With tree saturation free operation, the traffic to a congested output does not interfere with traffic addressed to other outputs. Stiff backpressure refers to flow control signaling of a source node to start or stop sending data.

[0011] The lack of non-blocking operation and stiff back-pressure is not a problem for multicomputer systems, because multicomputer traffic is self-throttling. After a processor has sent a small number of messages or memory requests (typically 1 to 8), it cannot send any further messages until it receives one or more replies. Thus, when the network slows down because of blocking or congestion, the traffic offered to the network is automatically reduced as the processors stall, awaiting replies.

[0012] A switch router, on the other hand, is not self-throttling. If some fabric links in the network become blocked for congested, the offered traffic is not reduced. In general, fabrics are designed with sufficient link capacity to offer low delay transit of packets through the fabric to

random destinations. With normal traffic, packets thus transit the fabric with little congestion. Accordingly, a packet is injected into the fabric assuming that a packet will be forwarded across the fabric at the maximum injection rate. This is known as speculative packet injection, because the injection of a packet is started without prior knowledge of the congestion state of links along the path or knowledge of the buffer availability state at the destination into which the packet is to be stored. Because of this, a switch router implemented with an unmodified multicomputer interconnection network is likely to become tree-saturated, and deny service to many nodes not involved in the original blockage.

[0013] Consider the situation of link based tree saturation illustrated in FIG. 4. A single node in a 2-dimensional mesh network, node (3,3) labeled A, is overloaded with arriving messages. As it is unable to accept messages off the channels at the rate they are arriving, all four input fabric links to the node, (B,A), (C,A), (D,A), and (E,A), become congested and are blocked. Traffic arriving at nodes B through E that must be forwarded across these blocked links cannot make progress and will back up along the edges into nodes B through E. For example, traffic into node B backs up along (F,B), (G,B), and (H,B). If the blockage persists, the links into F through H and related nodes become blocked as well and so on. If the overload on node A persists, eventually most of the links in the network will become blocked as a tree of saturation expands outward from node A. The major problem with tree saturation is that it affects traffic that is not destined for node A. For example, a packet from (1,4) to (5,3) may be routed along a path (dotted line) that includes (F,B) and (B,A). Since these links are blocked, traffic from node (1,4) to node (5,3) is blocked even though neither of these nodes is overloaded.

[0014] Previously, tree saturation and deadlock in fabrics implementing IP switch routers were addressed using destination based virtual networks (DBVNs), which are described in more detail in PCT Patent Application Ser. No. PCT/US98/16762, entitled "Router with Virtual Channel Allocation," filed Aug. 20, 1998, and published as WO99/11033, as well as U.S. patent application Ser. No. 08/918, 556, entitled "Internet Switch Router," filed Aug. 22, 1997. Both PCT Patent Application Ser. No. PCT/US98/16762 and U.S. patent application Ser. No. 08/918,556 are incorporated by reference in their entirety. A destination based virtual network set includes a virtual network implemented for each priority (e.g., high or low priority) per destination node in the fabric.

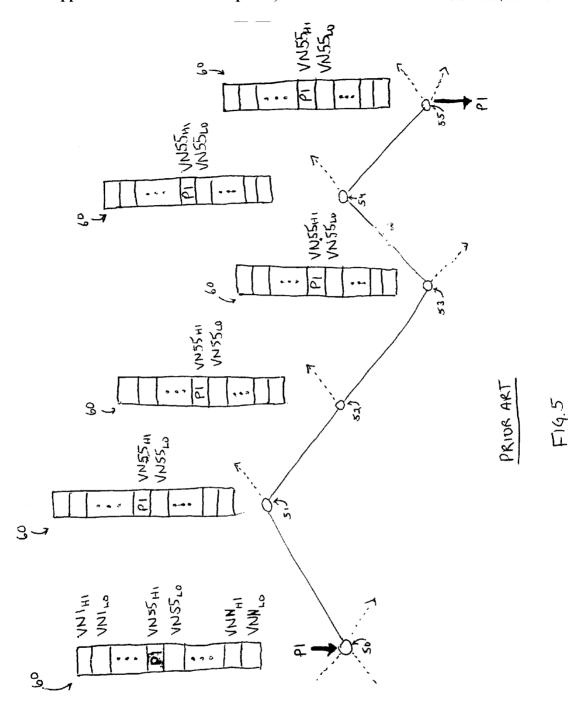

[0015] FIG. 5 illustrates packet traversal through a fabric implementing destination based virtual networks. Destination based virtual networks are implemented with a fixed number of dedicated buffer resources 60 at each fabric router, such as nodes 50 through 55. A virtual network is implemented for per destination node per priority. Control structures, such as packet queues, (not shown) are used to manage the flow of packets through each virtual network (i.e., VN1<sub>HI</sub>, VN1<sub>LO</sub>). . . VNN<sub>HI</sub>, VNN<sub>LO</sub>). Packets are forwarded across the fabric, for example, on a high or low priority virtual network associated with a particular destination node. At each hop along a path through the fabric, a packet is temporarily stored in buffers dedicated to the virtual network being traversed. Referring to FIG. 5, a packet P1 of high priority traverses the fabric to destination node 55 over a path of fabric routers on virtual network,

VN55<sub>HI</sub>. At each hop along the path, the packet is temporarily stored in dedicated buffers corresponding to virtual network, VN55<sub>HI</sub>. Since buffer resources are dedicated to each destination based virtual network, deadlock is impossible and packets experience congestion only when the virtual network on which they are traversing is congested. Thus, packets bound for uncongested destination nodes are allowed to flow past packets bound for congested nodes.

[0016] However, since dedicated buffer resources and control structures are required for every virtual network, destination based virtual networks are difficult to scale for very large fabric sizes containing multiple ports and priorities. In particular, to support per egress port priority flow control, dedicated buffer resources and control structures are required per destination node per egress port per priority. For example, a 3024 node fabric implementing 24 fabric egress ports per node with 2 priorities per fabric egress port (eg., high and low) requires 145,152 virtual networks to be implemented. Since current ASIC technology only allows about 500-1000 virtual networks to be implemented, the existing tree saturation avoidance scheme cannot scale to such large fabrics.

[0017] Embodiments of the present invention provide an interconnection network including routers interconnected by links. Packets traversing one or more hops across the links from various packet sources to various packet destinations. Subtrees of interconnected routers form source based virtual networks for each of the packet sources, while subtrees of the interconnected routers forming egress based virtual networks for each of the packet destinations. A packet is communicated from a packet source to a packet destination by traversing a source based virtual network of the packet source, transitioning into an egress based virtual network of the packet destination, and traversing the egress based virtual network to the packet destination. Packet sources and destinations may be ports, or individual data channels, such as Infiniband lanes, sharing the bandwidth of the ports. Alternatively, packet sources and destinations may be collective groups of data channels.

[0018] Each of the routers comprise dynamically assignable buffer resources for implementing these source based virtual networks and egress based virtual networks.

[0019] Additionally, each of the routers include memory implementing sets of queues for source based virtual networks and egress based virtual networks. The sets of queues are used for managing the transmission of packets over the virtual networks.

[0020] Embodiments of the invention may be incorporated into a fabric of an Internet router or multi-application switch router coupling different types of application specific modules. As a fabric, the interconnection network may be a vertex symmetric, direct network, such as a Gamma graph.

[0021] In more detail, a source based virtual network fans out from a common packet source over a subtree of interconnected routers through source based tunnels. Each of the source based tunnels extend less than the entire diameter of the interconnection network. Similarly, an egress based virtual network fans in to a common packet destination over a subtree of interconnected routers through egress based tunnels. Each of the egress based tunnels extend less than the diameter of the interconnection network. A packet is com-

municated from a packet source to a packet destination by traversing a source based tunnel associated with the packet source, transitioning into an egress based tunnel associated with the packet destination, and traversing the egress based tunnel to the packet destination.

[0022] The routers comprise dynamically assignable buffer resources for implementing source based tunnels as well as egress based tunnels. Each of the routers comprise memory implementing sets of queues for source based tunnels and egress based tunnels. The sets of queues for managing the transmission of packets over the tunnels.

[0023] Source based virtual networks and egress based virtual networks allow interconnection networks to scale to very large fabric sizes with multiple packet sources and destinations per node, while simultaneously preventing tree saturation and deadlock. Embodiments of the invention allow for such scalability because it reduces the number of control structures, such as packet queues, required to manage these virtual networks per fabric router. Furthermore, by implementing dynamic assignment of buffer resources to virtual networks as opposed to dedicated buffer assignment, efficient utilization of expensive memory resources is achieved.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0024] FIG. 1 illustrates a two dimensional torus array fabric used in prior art systems.

[0025] FIG. 2 illustrates packet traversal over path through a fabric.

[0026] FIG. 3 illustrates a typical switch element of a fabric router for forwarding data packets.

[0027] FIG. 4 illustrates tree saturation of a network.

[0028] FIG. 5 illustrates packet traversal through a fabric implementing destination based virtual networks.

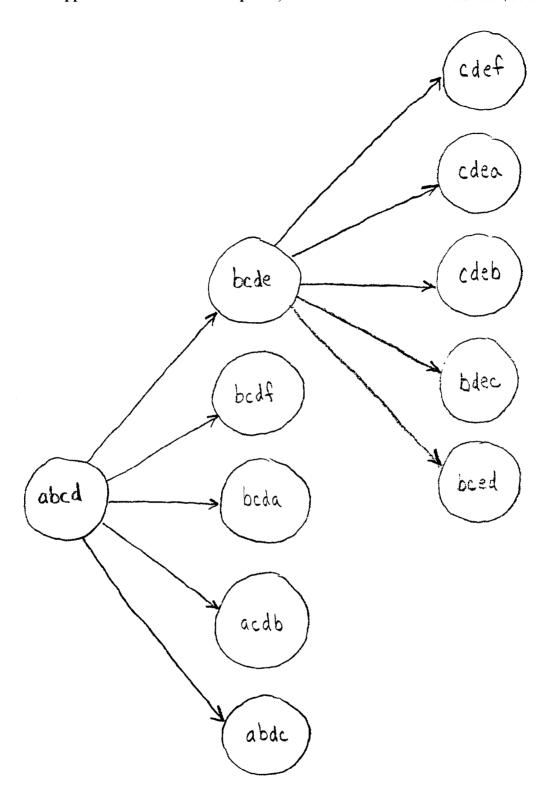

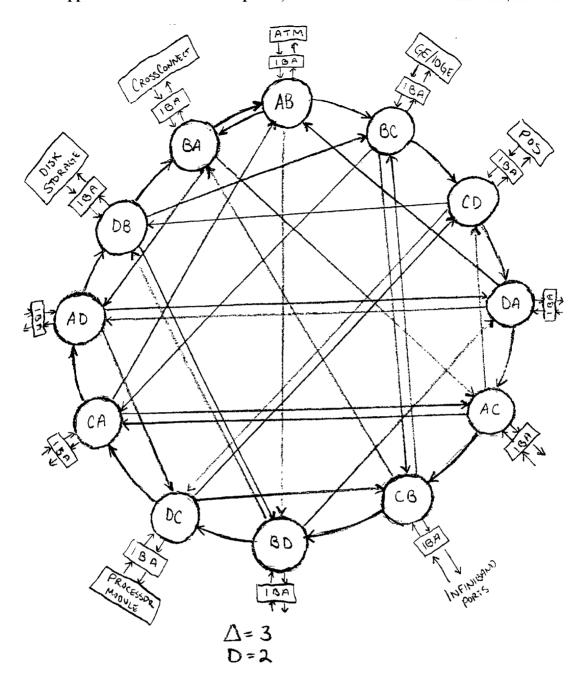

[0029] FIG. 6A is an example applying the Gamma graph adjacency rules.

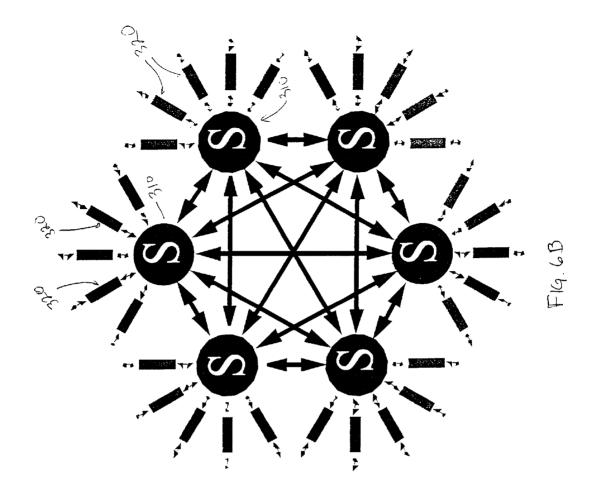

[0030] FIG. 6B illustrates a Gamma graph fabric requiring one hop to traverse the fabric according to one embodiment.

[0031] FIG. 7A illustrates a multi-application switch router employing a Gamma graph fabric interconnecting heterogeneous Application Specific Modules (ASMs) according to one embodiment.

[0032] FIG. 7B is a series of tables illustrating the adjacencies for each node within the Gamma graph of FIG. 7A.

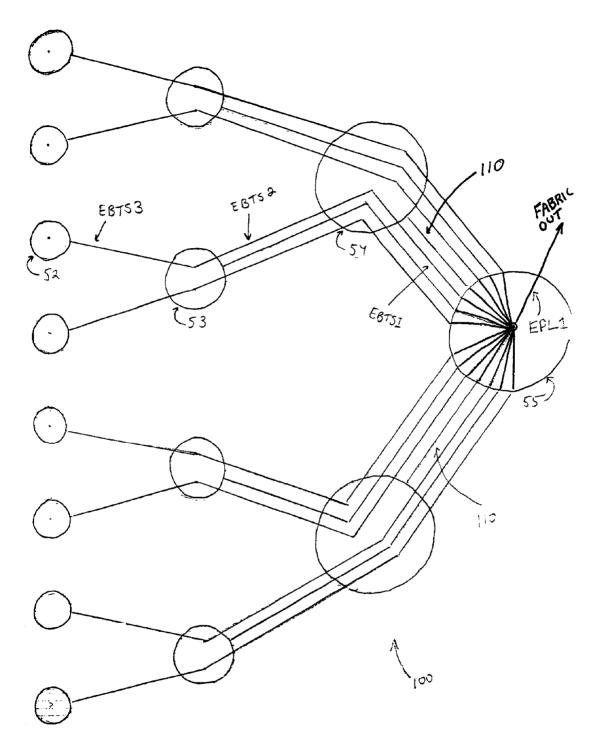

[0033] FIG. 8A illustrates a egress based virtual network according to one embodiment.

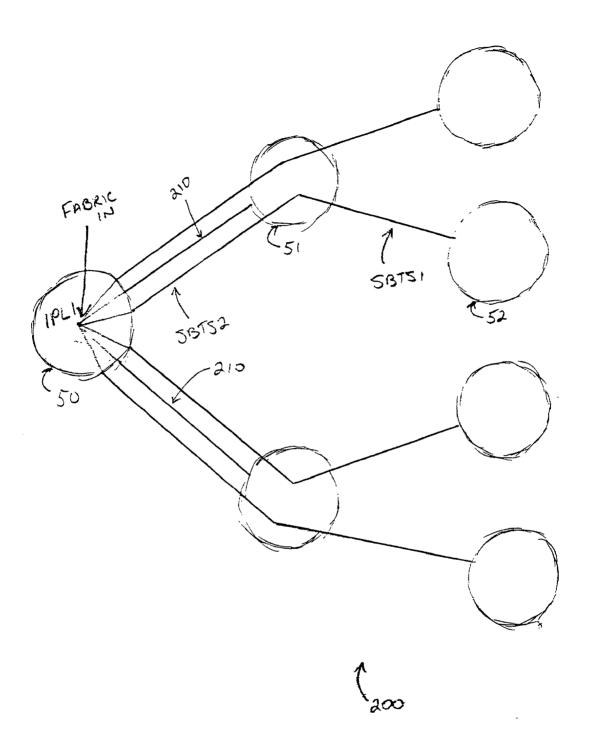

[0034] FIG. 8B illustrates a source based virtual network according to one embodiment.

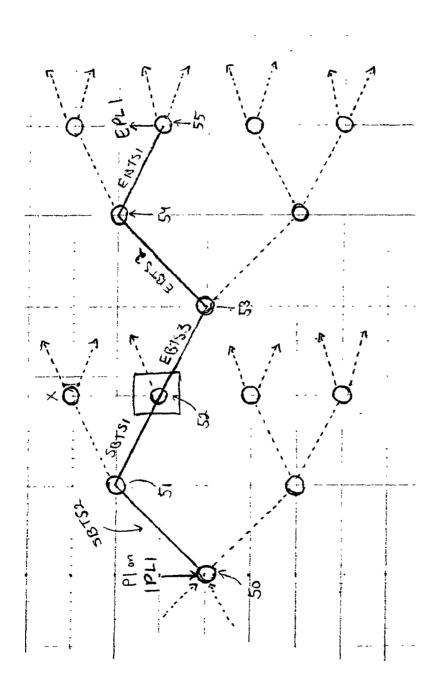

[0035] FIG. 9 illustrates packet traversal through the fabric over a source based virtual network and an egress based virtual network according to one embodiment.

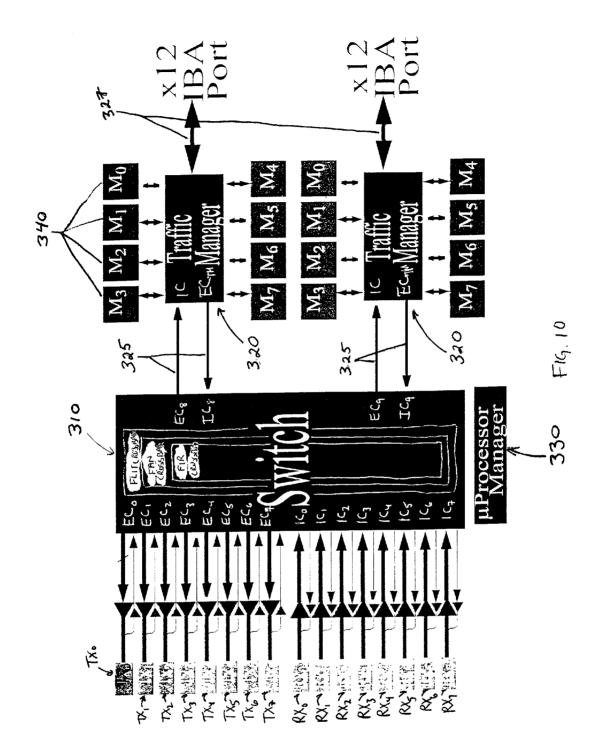

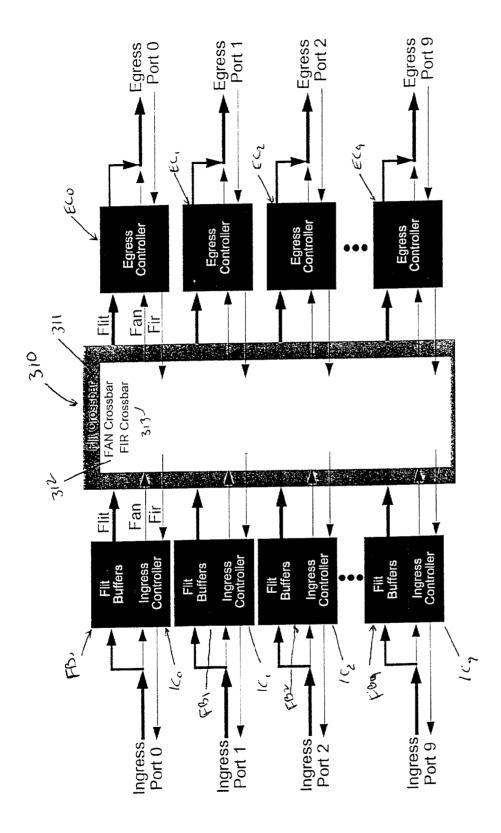

[0036] FIG. 10 illustrates the structure of a fabric router according to one embodiment.

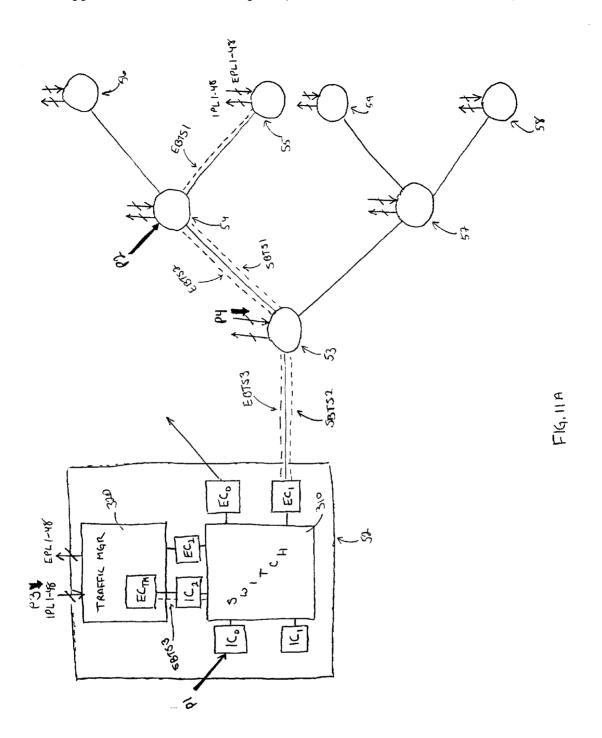

[0037] FIG. 11A is a diagram illustrating the management of tunnel segments from a fabric router according to one embodiment.

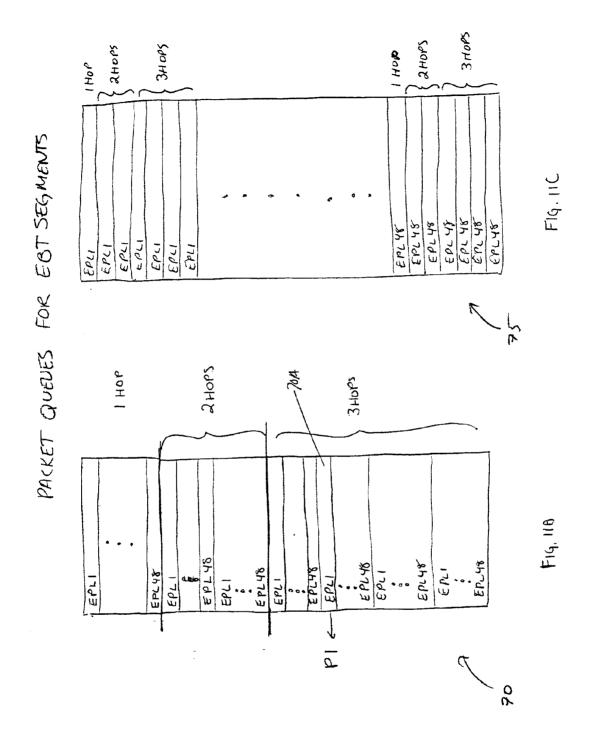

[0038] FIG. 11B and FIG. 11C illustrate alternative ways of grouping a set of EBT Segments according to embodiments of the invention.

[0039] FIG. 11D and FIG. 11E illustrate alternative ways of grouping a set of SBT Segments according to embodiments of the invention.

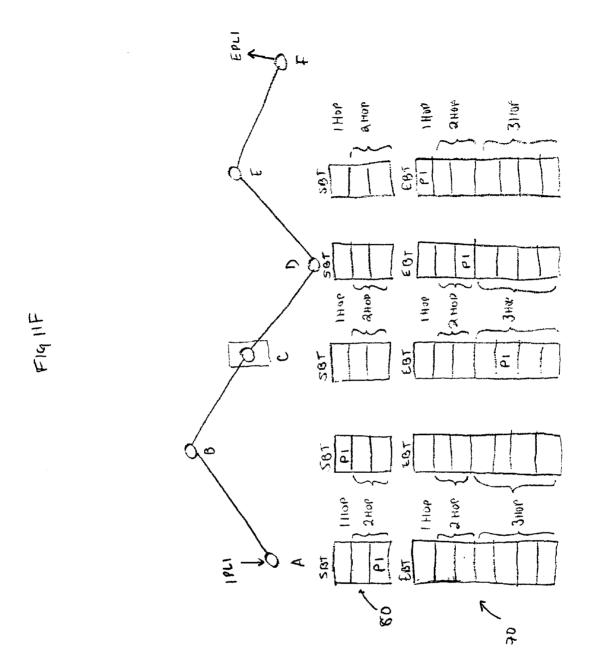

[0040] FIG. 11F illustrates packet traversal at each hop along a source based/egress based virtual network path according to one embodiment.

[0041] FIG. 12 illustrates a switch element according to one embodiment in more detail.

[0042] FIG. 13 is a table illustrating a set of control structures managed by a EgressController according to one embodiment.

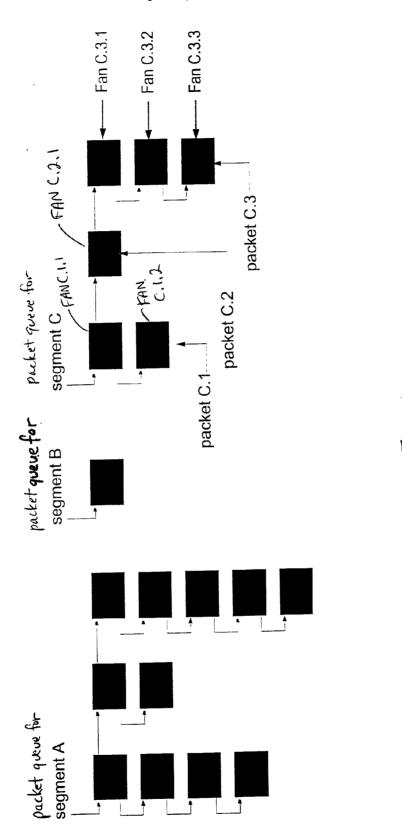

[0043] FIG. 14 illustrates the linking of FANs forming a packet and the linking of packets waiting on a segment for multiple segments according to one embodiment.

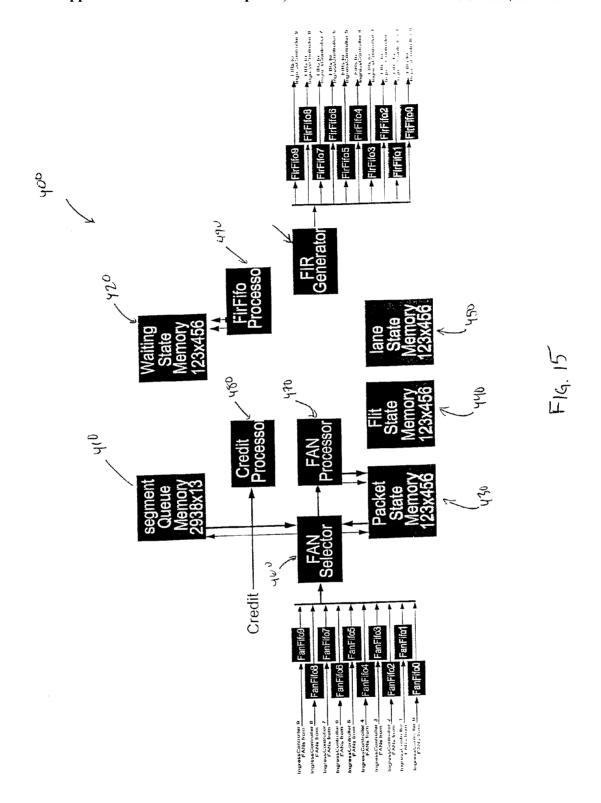

[0044] FIG. 15 illustrates the processing components and control memories of an EgressController according to one embodiment.

[0045] The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of preferred embodiments of the invention, as illustrated in the accompanying drawings in which like reference characters refer to the same parts throughout the different views. The drawings are not necessarily to scale, emphasis instead being placed upon illustrating the principles of the invention.

## DETAILED DESCRIPTION OF THE INVENTION

[0046] A description of preferred embodiments of the invention follows.

[0047] Tree saturation, particularly link-based tree saturation and egress port-based tree saturation, is a traffic condition negatively affecting the aggregate throughput rate of a fabric. As previously shown in FIG. 4, link-based tree saturation occurs when congestion at a link causes reduced throughput for traffic not passing across the congested link. Egress port-based tree saturation occurs when one oversubscribed egress port on a destination node causes reduced throughput for traffic bound to other egress ports on the same or other destination nodes. In fabrics not employing techniques to avoid link/destination based tree saturation, traffic still flows within the fabric but at a greatly reduced rate. Similarly, deadlock is a traffic condition where dependency loops form within the fabric. The throughput rate of traffic subject to a dependency loop is zero. When a deadlock condition occurs, it often expands to include all links within the fabric, thus, reducing the aggregate throughput rate of the fabric to zero.

[0048] Previously, destination-based virtual networks (DBVNs) were implemented to prevent deadlock and tree saturation during the operation of fabrics. However, destination based virtual networks are difficult to scale for very large fabric sizes containing multiple ports and priorities,

because a virtual network must be implemented and managed for every packet destination exiting the fabric. Therefore, as fabric size, port count, and priorities increases, the number of buffer resources and control structures increase exponentially.

[0049] Embodiments of the present invention allow for increased fabric bandwidth and scalability, while also preventing deadlock and tree saturation regardless of fabric size. An embodiment of the present invention is disclosed as it is applied to a Gamma graph interconnection network. Until now, Gamma graphs have not been exploited as a fabric topology for routers or switches. Moreover, by employing wormhole routing in conjunction with embodiments of the present invention, a stiff backpressure can be implemented regardless of fabric size. The utilization of Gamma graphs and the disclosures presented herein allow the implementation of extremely large scalable fabrics having a crossbar's desirable properties without its impossible scaling problems. However, it should be apparent that embodiments of the present invention may be applied to any type of interconnection network.

[0050] In 1988, Faber and Moore disclosed a family of directed graphs, including vertex symmetric directed graphs, for use as a multiprocessor interconnection network ("High Degree Low-diameter Interconnection Networks with Vertex Symmetry: the Directed Case," V. Faber and James W. Moore, Computing and Communications Division, Los Alamos National Laboratory, Los Alamos, N. Mex., the entire teachings of which are incorporated herein by reference). Gamma graphs are maximal for any value of A (switch radix) greater than D (diameter of fabric), interconnecting the largest number of nodes of any known directed graph.

[0051] A Gamma graph comprises nodes that interconnected according to a set of adjacency rules. The nodes within a Gamma graph are labeled with all permutations of words of length D characters where D is the fabric diameter, (e.g.  $X_1X_2X_3...X_D$ ). Characters in each label are members of a  $\Delta+1$  element alphabet, (e.g., a, b, c, d, e, and f for  $\Delta=5$ ). Hence the total number of nodes in a complete Gamma graph is calculated by the following equation:

$$(\Delta+1)\Delta(\Delta-1)\ldots(\Delta+2-D) \tag{1}$$

[0052] The following illustrates a set of adjacency rules for a node,  $X_1X_2X_3 \dots X_{D-1}X_D$ , within a Gamma graph:

$[\textbf{0053}] \quad \text{where } U_J \neq X_1, \, X_2, \, X_3, \dots \, X_D \text{ and } U_J \neq U_K \text{ when } J_K.$

[0054] One property of the links interconnecting nodes of a Gamma graph is that one of the links is bidirectional (e.g.,  $X_1X_2 \dots X_{D-1}X_D \rightarrow X_1X_2 \dots X_DX_{D-1}$ ), while the other  $\Delta$ -1 links are unidirectional. Another property of Gamma graphs is that there are  $\Delta$ -1 disjoint D+1 hop paths from any source to any destination node. Two paths are disjoint if they share no links. This property is used to both create massive fault tolerance and guarantee that strictly non-blocking routing is possible without prior connection knowledge.

[0055] FIG. 6A is an example applying the Gamma graph adjacency rules. Assuming a switch radix ( $\Delta$ ) of 5 and a diameter (D) of 4, the total number of nodes that can be interconnected in a Gamma graph, according to equation (1), is 360. The nodes are labeled with all permutations of words having a length of 4, and the characters in each label are members of a  $\Delta$ +1 element alphabet, (e.g., a, b, c, d, e, and f for  $\Delta$ =5). This results in 360 labeled nodes, such as abcd and bcde. As illustrated in FIG. 6A, the adjacent nodes that fan out from a particular node is determined by applying the set of adjacency rules set out above.

[0056] FIG. 6B illustrates a Gamma graph fabric requiring one hop to traverse the fabric according to one embodiment. In this configuration, five of the switch ports of each of the switches 310 are configured as access links and five are configured as fabric links. Each access link interconnects a switch 310 a Traffic Manager 320, which is a component managing the injection and extraction of packets from the fabric. Traffic Manager modules 320 can be added to a motherboard (on which the six switch elements reside) two at a time to increase the switching capacity from 24/6/2×1/4/12 ports to 360/120/30×1/4/12 ports. Note that the above configuration allows ASMs to be dual homed to achieve fault tolerance without resort to fabric replication.

[0057] FIG. 7A illustrates a multi-application switch router employing a Gamma graph fabric interconnecting heterogeneous Application Specific Modules (ASMs) according to one embodiment. For ease of illustration, the fabric has a switch radix ( $\Delta$ ) of 3 and a diameter (D) of 2 having 12 interconnected fabric routers, such as node AB. Examples of ASMs include Infiniband (IBA), Gigabit Ethernet (GE/10GE), CrossConnect, ATM, POS, disk storage subsystems, and processor modules. According to one embodiment, the fabric presents a plurality of industry standard Infiniband<sup>TM</sup> buses to the fabric exterior for coupling to each ASM. Infiniband™ facilitates the interoperability of diverse ASMs that are connected to the fabric creating complex systems. The design and construction of ASMs are known to a person skilled in the art. The Infiniband™ architecture is described in more detail in Infini- $\mathsf{band}^{\scriptscriptstyle\mathsf{TM}}$  Architecture Specification Volume 1 & 2, Release 1.0 COPYRIGHT ©1999, the entire contents of which are incorporated herein by reference.

**[0058] FIG. 7B** is a series of tables illustrating the adjacencies for each node within the Gamma graph of **FIG. 7A**. Since the fabric diameter is two, any destination node can be reached by any source node within two hops. The tables further illustrate some unique properties of Gamma graphs, particularly that there are  $\Delta$ -1 disjoint D+1 hop paths from any source to any destination node. Since the switch radix (A) is equal to 3 and the diameter is 2 hops, there are two disjoint paths involving three hops from any source to any destination node. Referring to **FIG. 7B**, a packet originating

from node AB can reach node CD in two hops via nodes BC and CD. However, it can also reach node CD in three hops via nodes BD, DC, and CD or nodes BA, AC, and CD. This property provides fault tolerance and guarantees strictly non-blocking routing without prior connection knowledge and without fabric replication. For example, if BC is oversubscribed processing packets, node AB can deliver a packet to node CD by selecting one of two alternative paths involving an additional hop.

[0059] In addition to providing a standard bus interface for Application Specification Modules, Infiniband™ can be used to achieve flexibility in port configurations. For instance, an Infiniband<sup>TM</sup> bus can be configured in one of four operating modes corresponding to different combinations of port count and port bandwidth. In its highest bandwidth port size, a single X12 port can be implemented (i.e., twelve 2 Gb/s segments transferring data in parallel in both directions). The three other configurations support two X6, three X4 and twelve X1 ports. The combination of maximal fabric sizes and the standard multi-port bus configurations facilitates the design of a very scalable and high bandwidth multi-application switch router. For example, according to equation (1), a Δ=8, D=4 Gamma graph fabric can have 3024 interconnected fabric routers. Assuming that two Infiniband™ buses are coupled to each fabric router and each Infiniband™ bus is configured to support twelve X1 ports, 72,576 fabric egress ports are served by a fabric needing only four hops to traverse the fabric.

[0060] Furthermore, Infiniband<sup>TM</sup> allows a port to channel data in logical flow controlled data channels called lanes. For example, if each port supports two lanes each, one lane can be configured to transfer audio and video, while the second lane transfers text. Thus, 145,152 egress port lanes (i.e., 72,576 ports×2 egress port lanes) can serve as destinations for packets traversing the fabric.

[0061] Under the destination based virtual network system, a virtual network for every egress port lane is implemented globally over the fabric. Every node contains dedicated buffer resources and control structures for implementing and managing each of the virtual networks. A packet traverses the fabric through a global virtual network corresponding to its destination egress port lane. At each hop along the fabric, the packet is temporarily stored in dedicated buffer resources corresponding to the virtual network being traversed. Thus, packets on one virtual network are not affected by packet congestion on another virtual network. Control structures at each fabric router, such as packet queues, are utilized to manage the flow of packets traversing each of the virtual networks.

[0062] However, implementing a destination based virtual network for a Gamma graph fabric as defined above would require dedicated buffer resources and control structures to manage 145,152 virtual networks. Particularly, each fabric router would require control structures to manage all 145, 152 destination based virtual networks per radix port. For example, fabrics having a switch radix equal to 8 and implementing a packet queue with a 13-bit pointer for each virtual network, over 15 million bits of on-chip memory would be required (i.e., 145,152 virtual networks×13-bits per queue pointer×8 outbound ports is approximately 15 million bits).

[0063] Embodiments of the present invention implement virtual networks requiring a reduced number of control

structures at each fabric router and dynamically assign buffer resources to individual virtual networks. According to one embodiment, the set of destination based virtual networks (DBVN) is partitioned into two virtual network sets, source based virtual networks (SBVNs) and egress based virtual networks (EBVNs). A packet is communicated through the fabric by traversing a source based virtual network and then traversing an egress based virtual network.

[0064] The source based virtual network corresponds with the source of the packet, while the egress based virtual network corresponds to the destination of the packet. According to one embodiment, the packet source may be a fabric ingress port, while a packet destination may be a fabric egress port. Since a port may support multiple data channels, a packet source may be an individual data channel (e.g., an Infiniband<sup>TM</sup> fabric ingress port lane) or a group of incoming data channels of a fabric ingress port. Similarly, a packet destination may be an individual data channel (e.g., an Infiniband<sup>TM</sup> fabric egress port lane) or a group of outgoing data channels of a fabric egress port.

[0065] Furthermore, a port, or channels thereof, may be associated with a priority (e.g., high or low priority). Therefore, a packet source may also correspond to the priority of a fabric ingress port, an individual channel, or a group of channels thereof. Similarly, a packet destination may correspond to the priority of a fabric egress port, an individual channel, or a group of channels thereof.

[0066] Both source based and egress based virtual networks are composed of "tunnels" through which packets are forwarded. According to one embodiment, a tunnel is a logical path through the fabric implemented with buffer resources dynamically assigned at each fabric hop. As a packet traverses each hop along a tunnel, packet buffers are dynamically assigned in the next hop fabric router to the tunnel allowing temporary packet buffering.

[0067] Since tunnels are logical paths, multiple tunnels can share the same physical path. Similarly, tunnels whose paths intersect may share one or more physical path segments. Therefore, tunnels prevent tree saturation and deadlock from occurring, because packets traversing different tunnels can bypass one another.

[0068] FIG. 8A illustrates an egress based virtual network comprising multiple tunnels according to one embodiment. The egress based virtual network (EBVN) 100 is a logical network implemented by a number of individual tunnels 110, referred to as egress based tunnels (EBTs). Each of the egress based tunnels is a logical path through the fabric to a common packet destination, such as fabric egress port lane EPL1. Each continuous line between two or more nodes represents an egress based tunnel, such as the continuous line extending through nodes 52, 53, 54, and 55. FIG. 8A illustrates an egress based virtual network for a single egress port lane. However, if each node has multiple egress port lanes, an egress based virtual network with a set of egress based tunnels is associated with each one. Thus, every packet destination has an egress based virtual network for funneling packets out of the fabric.

[0069] Egress based tunnels do not extend the entire diameter of the fabric. Therefore, source based virtual networks are implemented to provide logical paths into the fabric for injecting packets from a packet source into egress based virtual networks originating a number of hops within the fabric.

[0070] FIG. 8B illustrates a source based virtual network according to one embodiment. The source based virtual network (SBVN) 200 is a logical network implemented by a number of individual tunnels 210, referred to as source based tunnels (SBTs). Each of the source based tunnels is a logical path through the fabric from a common packet source, such as fabric ingress port lane IPL1 to a binding node within the fabric. A binding node allows packets traversing a source based tunnel to transition into one of the egress based tunnels fanning out from it. Each continuous line between two or more nodes represents the logical path of a source based tunnel, such as the continuous line extending through nodes 50, 51, and 52. FIG. 8B illustrates a source based virtual network for a single ingress port lane. However, if each node has multiple ingress port lanes, a source based virtual network with a set of source based tunnels is associated with each one. Thus, every packet source has a source based virtual network for injecting packets into the fabric.

[0071] FIG. 9 illustrates packet traversal through the fabric over a source based virtual network and an egress based virtual network according to one embodiment. For ease of illustration, FIG. 9 is a portion of a fabric having a switch radix (Δ) of 2 and a diameter (D) of 5. Labeled nodes 50, 51, 52, 53, 54, and 55 of FIG. 9 correspond to nodes 50, 51, 52 of FIG. 8A and nodes 52, 53, 54, and 55 of FIG. 8B.

[0072] To communicate a packet from any source to any destination, a packet traverses a source based virtual network and an egress based virtual network. A packet P1 is injected into a source based tunnel associated with the packet source IPL1. Since the egress based virtual network is two hops away from node 50, packet P1 is injected into a source based tunnel allowing it to traverse a logical path over the physical path encompassing nodes 50, 51, and 52. Packet P1 traverses the source based tunnel to its binding node endpoint 52, where the packet transitions into an egress based tunnel associated with packet destination EPL1. In FIG. 9, the egress based tunnel is a logical path over the physical path encompassing node 52, 53, 54, and 55. The packet then traverses the egress based tunnel until it reaches the packet destination exiting the fabric at EPL1.

[0073] A tunnel is constructed with a set of tunnel segments, each corresponding to a logical hop implemented over an access link (i.e., an internal link within a fabric router) or a fabric link. According to one embodiment, a tunnel segment is implemented with buffer resources dynamically assigned at a next hop fabric router. Dynamic allocation to tunnel segments provides for more efficient utilization of buffer resources. The dynamically assigned buffers allow the packet to be temporarily stored at the next hop after traversing the access or fabric link. Source based tunnels are constructed with source based tunnel segments (SBT Segments), while egress based tunnels are constructed with egress based tunnel segments (EBT Segments). Referring to FIGS. 9 and 8A, the source based tunnel extending through nodes 50, 51, and 52 is composed of two SBT segments, SBTS2 and SBTS1. Referring to FIGS. 9 and 8B, the egress based tunnel extending through nodes 52, 53, 54, and 55 is composed of three EBT segments, EBTS3, EBTS2, and EBTS1.

[0074] Each fabric router, such as nodes 50, 51, 52, 53, 54, and 55, manages sets of SBT Segments and sets of EBT

Segments. As a packet traverses each hop of a tunnel, a tunnel segment is selected to extend the tunnel to the next hop. Packets transit tunnel segments one packet at a time. Thus, when a packet transits one tunnel segment not terminating at the fabric egress port, the packet must bid for use on the next tunnel segment in order to extend the tunnel to the next hop. If the targeted next tunnel segment is busy or another packet wins the arbitration, the packet is added to a queue of packets waiting to traverse the selected tunnel segment. A packet queue is implemented for each tunnel segment managed by the fabric router.

[0075] FIG. 10A illustrates the structure of a fabric router according to one embodiment. Large fabrics typically cannot be packaged using the standard mother/daughter card arrangement employed in personal computers, rather a different packing scheme is required to allow the use to incrementally grow the fabric. Ideally, the fabric can grow by one switch module at a time. To allow maximum flexibility in scaling larger fabrics, one embodiment of a fabric router packages a switch element 310, one or more Traffic Managers 320, a microprocessor 330, and memory 340. With this node configuration, fabrics utilizing Gamma graphs as the fabric topology can be created supporting up to 76,896/25,732/6408 X1/4/12 ports.

[0076] Switch implementations can utilize either single or multiple chips. Single chip implementations having port bandwidths in the 20-30 Gb/s per port limit the radix of a switch to 10-14 due to pin limitations. Multi-chip switch implementations can be employed to increase the switch radix but dramatically increase the implementation complexity and increase costs for small fabrics. The bandwidth of each switch port typically is a few times the bandwidth of the largest single ingress flow. To support 10GE and OC192 data streams, the bandwidth requirement of a single switch port is typically in the 25-30 Gb/s range.

[0077] According to one embodiment, the switch element 310 includes three 10×10 crossbar switches, ten Ingress-Controllers, ten EgressControllers, and a pool of packet buffers (not shown). An IngressController manages the receipt of packets into the switch, while the EgressController manages the transmission of packets out of the switch. Each of the switch ingress ports is coupled to an Ingress-Controller terminating the downstream end of each ingress link. Similarly, each of the switch egress ports is coupled to an EgressController terminating the upstream end of each egress link. The main crossbar transfers packets or packet segments (e.g., flits) read from packet buffers to EgressControllers. The other two crossbars transfer control messages between IngressControllers and EgressControllers.

[0078] The switch element forwards packets received on any switch ingress port to a selected switch egress port. The switch is coupled to two Traffic Manager elements 320 via access links 325, which are typically electrical connections. Since two of the switch ingress and egress ports are utilized to connect to the Traffic Managers, the radix of this switch element is equal to  $\Delta$ =8 allowing eight fabric links to fan in and fan out from the switch interconnecting with other fabric routers. For small fabrics, the fabric links may be electrical connections. To allow maximum flexibility in interconnecting these switch modules, particularly for large fabrics, optical interconnections between fabric nodes may be implemented.

[0079] The Traffic Managers manage the injection and extraction of packets to and from the fabric. In addition, a Traffic Manager provides application wide ancillary services such as packet buffering and multicast as well as application specific services such as Random Early Discard and Packet Metering. The Traffic Managers are implemented as separate ASICs in order to maximize the radix ( $\Delta$ ) of the switch. However, the functionality of the Traffic Manager can be embedded into the switch element at the expense of severely limiting the switch radix. External memory chips 340 are utilized by the Traffic Managers for lookup tables, packet and control structure storage and monitoring structure storage.

[0080] Each Traffic Manager has a bus interface 327 to the external links of the fabric exterior. According to one embodiment, the bus interface is an InfinibandTm bus interface. This allows for interoperability of industry standard communications, processing and storage modules to interconnect with one another via the fabric. Although there is substantial motivation for providing an external interface which conforms with some industry standard bus, the links interconnecting switches to other switches (i.e. fabric links) and the links interconnecting switches to Traffic Managers (i.e. access links) need not conform with an industry standard. In particular, the links can be optimized to incorporate mechanisms for implementing wormhole routing and avoiding tree saturation as these features are useful only on intra fabric links.

[0081] A microprocessor 330 is normally incorporated on each node to implement the fabric management and monitoring functions. For example, the microprocessor may implement source routing and specify physical paths through the fabric between packet sources and packet destinations.

[0082] FIG. 11 A is a diagram illustrating the management of tunnel segments from a fabric router according to one embodiment. Tunnel segments are managed by a controlling agent, referred to as an EgressController, which handles the flow of packets through them. Each Traffic Manager includes an EgressController (i.e.,  $\mathrm{EC}_{\mathrm{TM}}$ ) at the head end of each access link interconnecting the Traffic Manager to a switch element, while each switch element includes an EgressController (e.g.,  $\mathrm{EC}_0$  and  $\mathrm{EC}_1$ ), at the head end of every fabric link interconnecting the switch to other switch elements in the fabric. An EgressController in a Traffic Manager manages SBT segments. Similarly, most EgressControllers in a switch element manage both SBT segments and EBT segments, with the exception of EgressControllers coupled to an access link.

[0083] Regarding switch elements, each EgressController manages a set of EBT Segments for all packet destinations, such as fabric egress port lanes, reachable from the Egress-Controller within a number of hops less than the fabric diameter (hops<D). According to one embodiment, the total number of EBT segments managed at any one EgressController equals  $N(1+\Delta+\ldots+\Delta^{D/2})$  as opposed to approximately  $N\Delta^D$  virtual channels of a DBVN system.

[0084] For example, in a D=4 fabric, an EBT Segment can be required for each egress port lane per destination node reachable from the EgressController in one, two, or three hops. Thus, the number of EBT segments managed in any EgressController is  $N(1+\Delta+\Delta^2)$  where N is equal to the

number of egress port lanes per node. Referring to FIG. 11A, assuming each fabric router services 48 fabric egress port lanes, EgressController EC<sub>1</sub> of node 52 manages an EBT Segment for each egress port lane (EPL1 through EPL48) one hop away at node 53, two hops away at nodes 54 and 57, and three hops away at nodes 55, 56, 58, and 59. Since the number of virtual channels managed in each fabric router in a destination based virtual network system would be approximately equal to  $N\Delta^4$ , embodiments of this invention result in a significant reduction in the number of control structures required at each EgressController.

[0085] EBT Segments may be managed with control structures, such as packet queues. FIG. 11B and FIG. 11C illustrate alternative ways of grouping a set of EBT Segment queues, 70 and 75, according to embodiments of the invention. For example, a set of EBT Segment queues 70 managed by a switch EgressController can be partitioned into groups having differing egress port lane identifiers, but sharing the same path to a common destination node as illustrated in FIG. 11B. Alternatively, the ensemble of EBT Segment queues 75 can be partitioned into groups having the same egress port lane identifier on different destination nodes as in FIG. 11C.

[0086] As a packet traverses each hop of an egress based tunnel, an EBT Segment is selected to extend the tunnel to the next hop. In particular, the IngressController receiving the packet selects a tunnel segment from information in the packet header and the fabric header prefixed to the packet. According to one embodiment, each EBT Segment is associated with an egress port lane identifier and a remaining hop count to the destination node serving the target egress port lane. The packet header provides the packet destination identifier, such as egress port lane EPL1, while the hop count and target destination node can be determined from the fabric header.

[0087] Referring to both FIGS. 11A and 11B, assume a packet P1 arrives at IngressController ICo of node 52 destined for EPL1 on node 55. The fabric header specifies remaining fabric hops encompassing nodes 53, 54, and 55. The IngressController IC<sub>0</sub> selects the tunnel segment EBTS3 corresponding to a remaining hop count of 3, a path corresponding to destination node 55, and lane EPL1. Ingress-Controller IC<sub>0</sub> notifies EgressController EC<sub>1</sub> that packet P1 is received and the selected tunnel segment identifier. Assuming tunnel segment EBTS3 is not busy and buffers are dynamically assigned to the tunnel segment at the next hop, the EgressController EC<sub>1</sub> forwards the packet to the Ingress-Controller of node 53 at the end of the fabric link. Referring to FIG. 11B, if the tunnel segment EBTS3 is busy or buffers are unavailable for packet buffering, the EgressController stores a reference to packet P1 in a packet queue 70A corresponding to EBT Segment EBTS3 until the tunnel segment is released or buffer resources become available at the next hop.

[0088] After packet P1 traverses the fabric link to the IngressController of node 53, the packet is now two hops away from destination node 55. The EgressController of node 53 also manages a set of EBT Segments similar to  $EC_0$  of node 52. Since the packet is two hops away from the packet destination, a different EBT Segment EBTS2 is selected corresponding to a remaining hop count of 2, a path corresponding to destination node 55, and lane EPLI. Simi-

larly, on the last hop, EBT Segment EBTS1 is selected corresponding to a remaining hop count of 1, destination node 53, and lane EPL1.

[0089] It should be noted that tunnel segments can be shared by different egress based tunnels. For example, in FIG. 11A, assume packet P2 arrives at node 54, (i.e. P2's binding node), at the same time packet P1 arrives at node 54. Even though both packets have the same destination, egress port lane EPL1 on node 55, both packets are traversing different EBTs. P2 traverses an egress based tunnel having one hop originating from binding node 54, while packet P1 traverses an egress based tunnel having three hops originating from binding node 50. However, since both packets are currently one hop away from the same packet destination, the same tunnel segment, EBTS1, may be shared to traverse the last hop. Therefore, if packet P1 requests tunnel segment EBTS 1 prior to packet P2, P2 will be referenced in a packet queue corresponding to the tunnel segment waiting for packet P1 to release the tunnel.

[0090] In another embodiment, tunnel segments may not be shared. Instead, individual queues would be implemented for each tunnel, that is, for each distinct path defined between a binding node and a destination channel (e.g., Infiniband™ lane) in the egress based virtual network. Such a configuration would decrease conflict between packets, but increase the number of packet queues per EgressController. The number of queues would still be less than the number of virtual channels managed in the prior destination based virtual network.

[0091] Egress based tunnels do not extend the entire diameter of a fabric, because the number of EBT segments managed at each EgressController would exceed the number of virtual channels managed in the destination based virtual network (DBVN) system. For example, if an EBT Segment were defined for each egress port lane reachable in one, two, three, four or five hops, then all possible virtual networks in a D=4 fabric supporting link failures are covered. However, this would require  $N(1+\Delta+...+\Delta^{D})$  segments per Egress-Controller, where N is the number of egress port lanes per node. Since the number of destination based virtual networks is typically less than  $N\Delta^D$ , simply extending the concept of EBT segments in a D=4 fabric to include four and five hop paths actually increases the number of tunnel segments and, thus, increases the number of control structures. For this reason, source based virtual networks are implemented to limit the number of required control structures for managing EBT segments.

[0092] By incorporating source based virtual networks (SBVNs), the low number of tunnel segments managed by each switch EgressController is maintained and tree saturation is still avoided. The SBTs of a source based virtual network provide logical paths into the fabric for injecting packets from a packet source into egress based virtual networks originating a number of hops within the fabric.

[0093] According to one embodiment, SBTs extend the reach of packet injection to egress based tunnels whose starting point is in a fabric router zero, one or two fabrics hops away from the source node. Therefore, if a fabric has a four hop diameter, a packet can traverse the fabric with one hop in a source based tunnel and three hops in an egress based tunnel. Similarly, in a situation where a link failure occurs in a Gamma graph fabric, an alternative path with an

additional hop can be traversed. Thus, in such a situation, a packet could traverse the fabric through a path with two hops in a source based tunnel and three hops in an egress based tunnel. Depending on the size of the fabric, SBTs may extend more than two fabric hops.

[0094] Regarding switch elements, each EgressController manages a set of SBT Segments for paths to binding nodes reachable from the EgressController within, for example, one or two hops away. Thus, the total number of SBT Segments managed at any one EgressController equals  $N(1+\Delta)$  where N is the number of fabric ingress port lanes per source node. For example, in a D=4 fabric, an SBT Segment is required for each binding node reachable from the EgressController in one or two hops per ingress port lane. Referring to FIG. 11A, this results in an SBT Segment associated with binding node 53 and binding nodes 54 and 57, which are one hop and two hops away respectively. If there are multiple ingress port lanes serviced by each node, there is a set of such SBT Segments for each one. in general, at any switch EgressController, the total number of tunnel segments is N(1+ $\Delta$ ) SBT segments and N(1+ $\Delta$ +...+ $A\Delta$ <sup>D/2</sup>) EBT segments, which is approximately N $\Delta$ <sup>D/2</sup> for large values of  $\Delta$ . This results in a total number of control structures being less than the control structures for the approximately  $N\Delta^D$  virtual channels of a DBVN system. Therefore, assuming a Δ=8, D=4 Gamma graph fabric having 48 ingress and egress port lanes, each fabric router would manage 3936 tunnel segments per EgressController, as opposed to 145,192 virtual channels per EgressController in a destination based virtual network system.

[0095] SDT Segments may be managed with control structures, such as packet queues. FIG. 11D and FIG. 11E illustrate alternative ways of grouping a set of SBT Segments queues, 80 and 85, according to embodiments of the invention. For example, assuming each fabric router services 48 ingress port lanes, the ensemble of SBT Segment queues 80 managed by each switch EgressController can be partitioned into groups sharing the same path to a common binding node as illustrated in FIG. 11D. Alternatively, the ensemble of EBT Segment queues can be partitioned into groups having the same ingress port lane identifier, but different paths to binding nodes as in FIG. 11E.

[0096] As a packet traverses each hop of a source based tunnel, an SBT Segment is selected to extend the tunnel to the next hop. In particular, the IngressController receiving the packet selects a tunnel segment from information in the packet header and the fabric header prefixed to the packet. According to one embodiment, each SBT Segment is associated with a packet source identifier, (e.g., fabric ingress port lane identifier) and a remaining hop count to a binding node of a particular egress based virtual network. The packet header provides the packet source identifier, such as ingress port lane IPL1, while the hop count and target binding node can be determined from the fabric header.

[0097] As described previously, the Traffic Manager may be coupled to the switch element by an access link. Thus, packets must traverse an internal hop from the Traffic Manager to the switch element. Accordingly, the Egress Controller in each Traffic Manager (EC<sub>TM</sub>) manages a set of SBT segments corresponding to tunnels extending binding nodes within 0, 1 or 2 hops of the EgressController. Thus, the EgressController in the Traffic Manager supports a total

of  $N(1+\Delta+\Delta^{D/2})$  SBT segments where N is equal to the number of ingress port lanes per node.

[0098] Referring to FIG. 11A, assume a packet P1 arrives from an external link on fabric ingress port lane IPL1 of node 52. The packet is received by the Traffic Manager 320 which appends a fabric header to the packet specifying each hop through the fabric to the packet destination as well as a hop count. The hop count indicates the relative number of hops remaining to a binding node that allows packets to transition into the target egress based virtual network. Typically the path is specified as a sequence of switch egress port identifiers.

[0099] According to one embodiment, the packet may be segmented into fixed size data blocks, referred to as flow control units or "flits," in order to reduce buffering requirements within the switch and latency. A packet can be partitioned into head, body, and tail flits. Alternatively, for smaller packets, the packet can be converted into a single flit, referred to as an OnlyFlit, including the entire packet with a flit header.

[0100] The EgressController ECTM injects the packet P3 (or head flit) into one of the managed SBT Segments corresponding to the packet source, IPL1. The selected SBT Segment SBTS3 originates a source based tunnel to a binding node endpoint. Assuming that the fabric header specifies a path encompassing nodes 53, 54, 55, etc. and a remaining hop count of 3, the packet will be injected into an SBT Segment corresponding to a remaining hop count of 3, a path corresponding to binding node 54, and lane IPL1. The remaining hop count from binding node 54 is three, because there is one additional internal hop over the access link coupling the Traffic Manager 320 to the IngressController IC, of switch 310. Assuming buffer resources are dynamically allocated to the selected tunnel segment, the packet traverses the access link to IngressController IC.

[0101] The IngressController IC<sub>2</sub> selects the SBT Segment SBTS2 corresponding to a remaining hop count of 2, a path corresponding to binding node 54, and lane IPL1. Ingress-Controller IC<sub>2</sub> notifies EgressController EC<sub>1</sub> that packet P3 is received and provides the selected tunnel segment identifier. Assuming the tunnel segment is not busy and buffers are dynamically assigned to the tunnel segment at the next hop, the EgressController EC<sub>1</sub> forwards the packet to the IngressController of node 53 at the end of the fabric link. Referring to FIG. 11D, if the tunnel segment SBTS2 is busy or buffers are unavailable for packet buffering, the Egress-Controller EC<sub>1</sub> stores a reference to packet P3 in a packet queue 80A corresponding to SBT Segment SBTS2 until the tunnel segment is released or buffer resources become available at the next hop.

[0102] After packet P1 traverses the fabric link to the IngressController of node 53, the packet is now one hop away from binding node 54. The EgressController of node 53 also manages a set of SBT Segments similar to EC<sub>1</sub> of node 52. Since the packet is one hop away from the binding node 54, a different SBT Segment SBTS1 is selected corresponding to a remaining hop count of 1 and lane IPL1. Again, assuming the tunnel segment is not busy and buffer resources are dynamically allocated to SBTS1 at the next hop, packet P3 traverses the fabric link to the IngressController of node 54. At node 54, the packet will transition into an appropriate egress based virtual network as described previously.

[0103] Like EBT Segments, SBT Segments can be shared by different source based tunnels. For example, in FIG. 11A, assume packet P4 from fabric ingress port lane IPL1 is received by an IngressController IC<sub>2</sub> of node 53, (i.e. P4's source node), at the same time packet P3 is received by another IngressController at node 53. Even though both packets are targeted for the same binding node (i.e., node 54) and have the same ingress port lane identifier IPL1 on node 55, both packets are traversing different SBTs. P3 traverses a source based tunnel having three hops (one internal hop and two fabric hops) originating from source node 52, while packet P4 traverses a source based tunnel having one hop originating from source node 53. However, since both packets have the same ingress lane identifier IPL1 and are currently one hop away from the same target binding node, the same tunnel segment, SBTS1, may be shared to traverse the last hop. Therefore, if packet P4 requests tunnel segment SBTS1 prior to packet P3, P3 will be referenced in a packet queue 80A corresponding to the tunnel segment waiting for packet P4 to release the tunnel.

[0104] In another embodiment, SBT Segments may not be shared. Instead, individual queues would be implemented for each tunnel, that is, for each distinct path defined between a source node and a binding node. Such a configuration would decrease conflict between packets, but increase the number of packet queues per EgressController. The total number of SBT/EBT Segment queues would still be less than the number of virtual channels managed in the prior destination based virtual network.

[0105] FIG. 11F illustrates the packet traversal at each hop along a source based/egress based virtual network path according to one embodiment. Assuming each node has one fabric ingress port and one fabric egress port, a packet P1 is initially injected into a source based tunnel segment corresponding to an SBT that is two hops away from its binding node C. The packet may be temporarily queued in one of the packet queues 70 selected by the ingress lane number and hop count. After packet P1 traverses the fabric link to node B, P1 is now one hop away from binding node C. Therefore, packet P1 is assigned to an packet queue corresponding to a SBT Segment one hop away from the target binding node. Once packet P1 reaches binding node C, it transitions into an EBT Segment corresponding to its target destination that is three hops away. As packet P1 traverses the egress based tunnel originating from node C, it may be temporarily queued in packet queues corresponding to the packet destination and the number of remaining hops to reach it. Buffer resources (not shown) are dynamically allocated to the selected tunnel segment as the packet traverses the tunnel. This provides more efficient utilization of expensive buffer resources.

[0106] An event driven routing approach, such as that described in PCT Patent Application Ser. No. PCTIUS98/16762, entitled "Router with Virtual Channel Allocation," filed Aug. 20, 1998, and published as WO99/11033, may be extended to support embodiments of the present invention with source based virtual networks and egress based virtual networks.

[0107] Packets are typically transported across a fabric as an ordered sequence of flits using a technique called wormhole routing. With wormhole routing, the head flit of a packet traverses a predetermined path across the fabric. As

the head flit traverses each switch element, buffer and control resources needed to forward the packet across the switch are allocated to the packet. The remaining flits of the packet transit the fabric via the path established by the head flit using the resources reserved by the head flit. As the tail flit of a packet transits a Switch element, the resources allocated by the head flit are released for reallocation.

[0108] In more detail, packets forwarded through the fabric typically range in size from 60 bytes to 4k bytes. Packets received at an Infiniband ingress port are stripped of extraneous information and then stored in a memory controlled by the Traffic Manager.

[0109] As a packet is injected into a Source Based Tunnel (SBT), a header is prefixed to the packet and the augmented packet is segmented into 40-byte flits. Longer packets are transported across the fabric as an ordered set of head flit, zero or more body flits and ending with a tail flit. The head and body flits typically contain 40-bytes. To minimize fragmentation losses, the tail flit of a packet can contain 40, 50, 60 or 70 bytes. Packets shorter than 71-bytes are transported across the fabric as a OnlyFlit. OnlyFlits are equivalent to a head flit and tail flit combined. An OnlyFlit can contain 40, 50, 60 or 70 bytes including the packet header. A four byte flit header is transported along with each flit. The flit header contains multiple fields including a next hop field and a hop identifier.

[0110] As previously stated, destination based virtual networks facilitated the forwarding of packet across a fabric on a high or low priority virtual network associated with a particular destination node. For small fabrics having a single egress port and two priorities, this scheme both prevents deadlock and tree saturation. At each fabric ingress port, a fixed number of flit buffers was associated with each virtual network. The number of flit buffers associated with each fabric was dictated by the forwarding velocity required. Typically 4-6 flit buffers were required to achieve link rate forwarding rate. Simulations of this scheme demonstrated deadlock and tree saturation free operation. The simulations also demonstrated under-utilization of the expensive flit buffer resources. To allow larger fabric sizes and up to 48 egress port lanes per node, the number of buffers would need to increase by a prohibitive two orders of magnitude. Thus while the invention of virtual networks solves the problems of tree saturation, the system is difficult to scale for very large fabrics.

[0111] Since with normal traffic loads, only a few packets sourced from each node are traversing the fabric, embodiments of the present invention dynamically assign buffer resources to source based and egress based virtual networks (i.e., EBT Segments and SBT Segments) upon request.

[0112] To decouple flit buffer resources from virtual networks, embodiments of the invention associate a set of lanes with each link. Each lane has an associated pair of flit buffers at the downstream end of the link. To increase the forwarding velocity, buffers from a pool of flit buffers can be dynamically used by a lane up to a configurable maximum number. With normal traffic conditions, only a small number of lanes will be in use at one time so that each lane can utilize the maximum number of flit buffers.

[0113] Lanes are partitioned into lane groups assigned to each path hop. Lane groups prevent deadlock, which occurs

in situations where dependency loops come into existence with a only single group of lanes dynamically assignable to virtual networks. The localized deadlock created by a single dependency loop typically causes a system wide deadlock as more and more links exhaust their pool of lanes. Therefore, by partitioning lanes into lane groups, deadlock is prevented because dependency loops can never be formed. Only lanes in lane group K can be assigned to transport packets K hops away from their destination. Implementing approximately 30-40 lanes in each lane group reduces the probability of lane exhaustion to extremely low values even for the largest fabric sizes.

[0114] Unlike virtual networks which have global scope, lanes are strictly local. A lane in lane group K is used to transport a packet across the associated link if and only if the packet is K hops away from its destination. Thus the lane identifier used on successive links are always different. Since lanes within a virtual network are dynamically assigned to a partially formed tunnel, two packets traversing the same virtual network over the same path will typically employ a different lane for each hop for each packet.

[0115] Lanes are managed and allocated by an EgressController at the head end of each link. Like tunnel segments, lanes have the concept of being busy (i.e., assigned to a packet transport) or non-busy (i.e., available to be assigned to a packet). Lanes are assigned to partially formed tunnels as the head flit of the packet arrives at a node. Typically, a lane is released when the tail flit of a packet is forwarded from the downstream flit buffer memory.

[0116] A packet is transported from the EgressController at the upstream end of a link to an IngressController at the downstream end of a link utilizing the control structures associated with a particular lane. Such control structures is described in more detail with respect to FIG. 13.

[0117] FIG. 12 illustrates a switch element according to one embodiment in more detail. In addition to control structures, two flit buffers (e.g., FB<sub>0</sub>) in the flit memory associated with the IngressController (e.g., IC<sub>0</sub>) are dedicated to the lane. According to one embodiment, 128 lanes are implemented partitioned into 3, 4, 5 or 6 lane groups. Flit memory holds 512 40-byte flits of which 256 are dedicated to particular lanes and 256 are dynamically assignable to lanes.

[0118] Packets arrive at an ingress port as an ordered sequence of flits. While there may be instances where all the flits of one packet arrive back-to-back at an ingress port, the typical case has flits of multiple packets arriving at an ingress port in a relatively uncoordinated manner.

[0119] A flit header is forwarded with each flit payload. Each header contains a 7-bit lane field to identify the lane, a four-bit next hop field and a 3-bit flit type field. The lane identifier allows a downstream IngressController to select the lane's control structure. The type field allows checking for flit sequencing errors. For example, two head flits having the same lane number cannot arrive back-to-back over the same lane.

[0120] An upstream EgressController will never forward a flit downstream unless there is an empty flit buffer into which the flit can be stored. Thus it is the upstream Egress-Controller which manages the downstream flit memory. To minimize the number of bits transferred in each flit header,

the address of the one or two flit buffers into which the flit will be stored is not forwarded in the flit header. Rather the address is dynamically created by the IngressController as the flit arrives.

[0121] As each flit arrives, the IngressController looks up the lane's state structure and then synthesizes a Flit Arrival Notification (FAN) message. The created FAN is immediately forwarded to the EgressController specified in the flit header's next hop field. The flit is stored in one of the dedicated buffers assigned to the lane or into one of the pool buffers usable by all lanes. The lane's state structure is updated immediately following the arrival of the last 10-bytes of the flit.

[0122] According to one embodiment, each flit header contains a flit checksum. If a checksum violation is detected by the IngressController, it returns a message over the credit segment (e.g., bandwidth channeling control messages from the IngressController to the upstream EgressController to the head-end) indicating which flit was received in error. All subsequent flits after receiving an errored flit are dropped until a retransmission code is detected.